| Quantity | 3+ units | 10+ units | 30+ units | 50+ units | More |

|---|---|---|---|---|---|

| Price /Unit | $336.77 | $329.89 | $319.59 | $305.84 | Contact US |

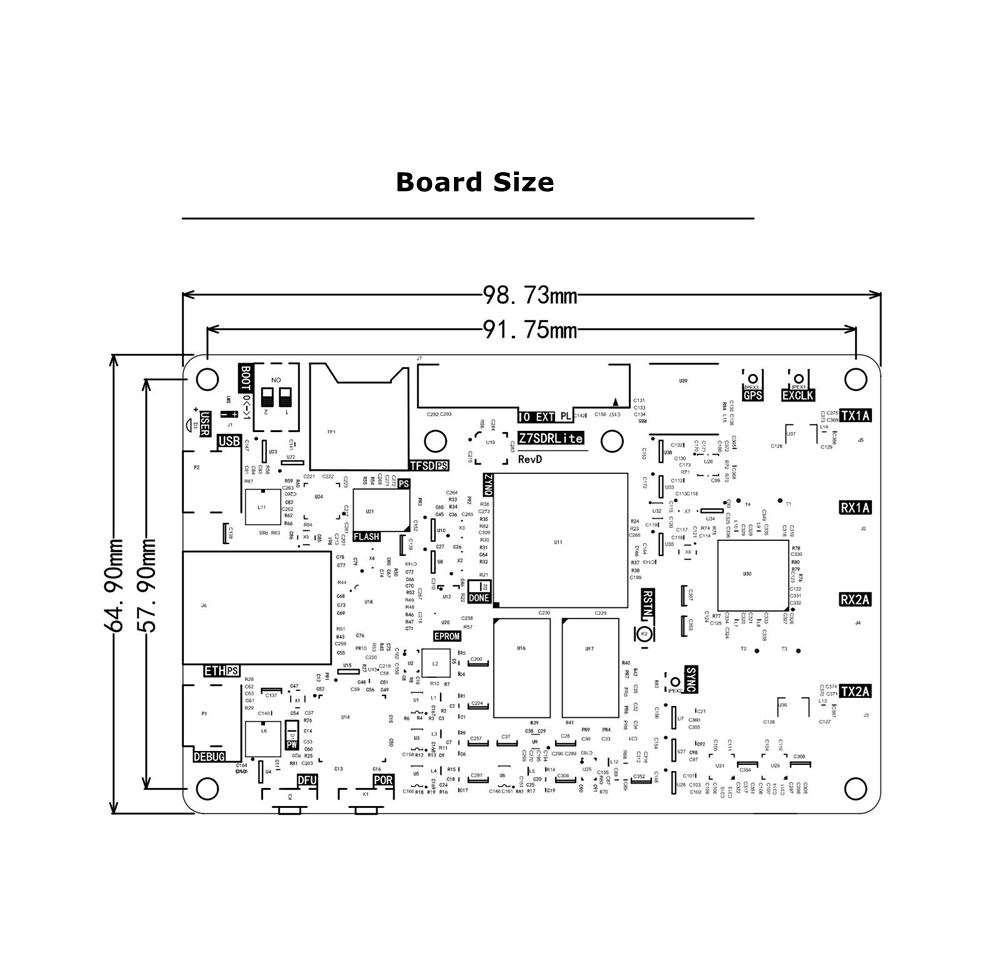

Z7SDRLite 9361 Professional Version Software Defined Radio Development Board XC7Z020 Compatible with PlutoSDR (Metal Shell)

Main Chip Parameters:

- Master chip model: XC7Z020-2CLG484I

- Chip level: industrial

- Clock recommended maximum speed: FPGA PLL/MMCM recommended maximum 628M

- PS application processor model: for ZYNQ onboard hardcore processor, dual core Cortex-A9, main frequency of 766M

- DDR specification model: 1024MByte (1GB), 32 bit width, 1066M data rate, MT41K256M16TW-107

- Logic unit: 85K

- Lookup table: 53200

- DSP unit multiplier: 220

- Trigger (FlipFlops): 106400

- Ram: 4.9MBit

- Component temperature range; industrial -40 to 85℃

- Speed level: -2

Z7SDRLite functional interface description:

- Development board power supply: power supply through USB/DEBUG Type-C, 5V input; device power consumption about 3 - 6W (different applications and firmware have varying power consumption)

- Development board clock: 33.33M (PS), 50M (PL), 40M (VC-TCXO-0.5PPM)

- External clock: AD936X reserved external clock input, IPEX1 interface

- USB interface: one USB interface, support USB2.0 virtual network port

- Serial port/JTAG: 1 x FT2232HQ 2-in-1, support UART/JTAG

- Ethernet interface: 1 x PS gigabit Ethernet, RTL8211E

- Expansion IO port: 1 x BTB connector, model of X0802WVS-60AS-LPV01, lead out 40 IOs, 4 pair of differential/32 single-ended, voltage can be modified

- LED and button: POR reset/PL_RSTN/DFU button/USR/PWR/DONE indicators

- Boot setting switch: one BOOT toggle switch for boot setting

- Onboard FLASH: 32MBytes, model of MT25QL256ABA1EW9-0SIT

- SD interface: one SD interface of TF card slot, support SD boot

- GPS module: onboard a MAX M10S GPS module

- EEPROM: onboard a 24C02, PL terminal

- Synchronization: reserve SYNC and IPEX1 of AD9361; ignore AD9363, not supported

- Note 1: Expansion IO port support 4 pairs of differential and 2.5V LVDS_25.

- Note 2: 32 single-ended IOs. Differential wiring is not supported.

- Note 3: The default voltage for expansion IO ports is 2.5V, which can be modified to 1.8V/2.5V/3.3V by oneself.

AD9361 Parameters:

- Master chip model: AD9361bbcz

- ADC/DAC resolution: 12Bit

- Signal data bit width: 200K - 56MHz

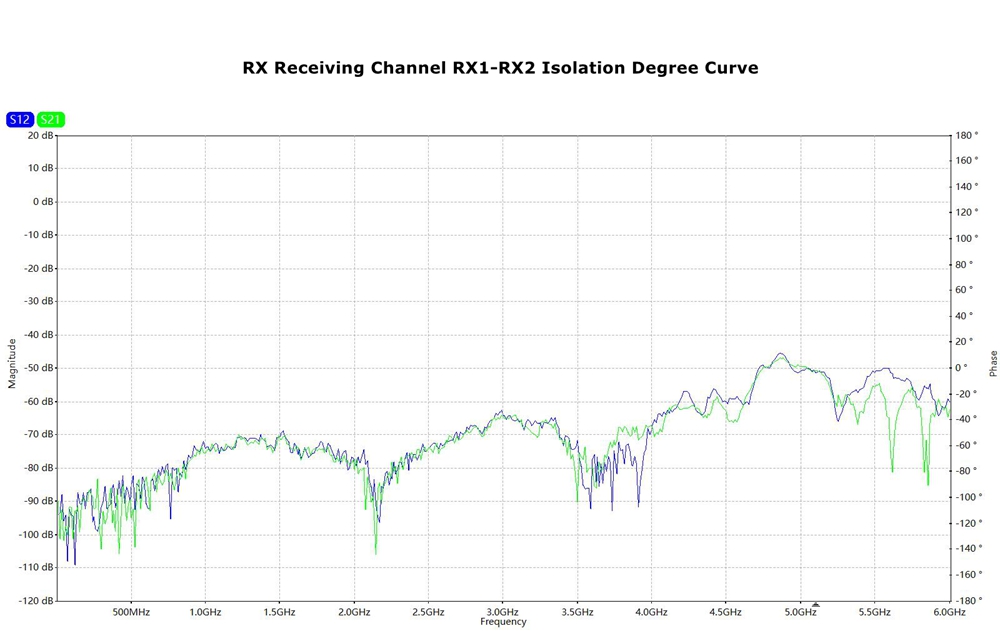

- Channel number: 2 receiving and 2 transmitting/2x2; each channel support for IQ

- Transmitting RF range: 47MHz - 6.0GHz

- Receiving RF range: 70MHz - 6.0GHz

- Receiving noise ration: 2dB (800MHz LO)

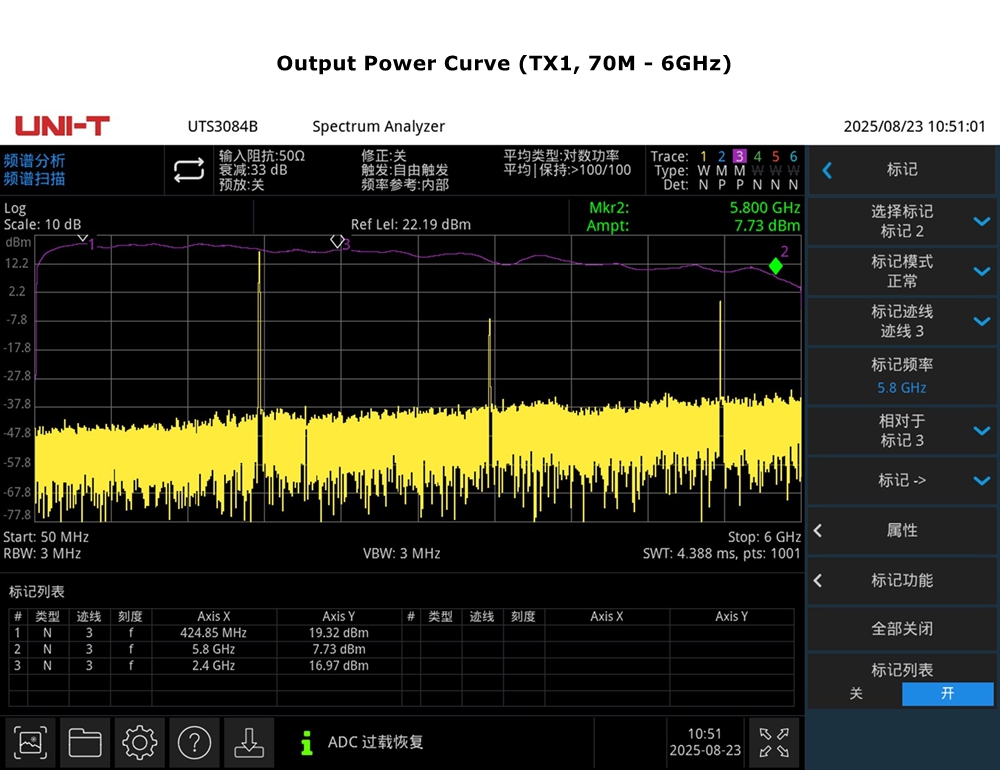

- Transmitter performance:

TX EVM: ≤-40dB

TX noise: ≤-157dBm/Hz

TX monitor: dynamic range≥66dB, precision = 1dB

- Local oscillator step length: 2.4Hz max.

- Synchronization: support multiple components SYNC synchronization

- Gain control: support automatic gain/manual setting gain

RF Functional Interfaces Parameters:

- Antenna interface: SMA female connector

- Clock: 1pcs 40MHz/0.5ppm VC-TXCO

- External clock: support AD936X external clock

- RF LDO linear power supply: wireless LO power supply 1.3V/4A power supply 2-channel RF LDO; PSRR: 40dB (500kHz); noise: 4.4uVRMS (0.8V)

- Impedance control: RF front-end to SMA antenna, control 50ohms microstrip line

- Front-end balun: 1:1, TCM1-63AX+, 10M - 6GHz

- TX power amplification: TX channels all equipped with power amplification output, about 15dB/800MHz, amplifier noise ratio is about 3.8dB

- Onboard GPS PPS precision: RMS 30ns

Firmware Boot and Sampling Rate:

- For PlutoSDR firmware: support 1R1T, 5MSPS, using USB virtual Ethernet port

- For PlutoSDR firmware: factory FLASH firmware

- For FMCOMMS3 firmware: support 2R2T, 10MSPS, using 1000M Ethernet port

- For FMCOMMS3 firmware: SD card boot, you need to prepare SD card by yourself to write mirror image

Package Included:

- 1 x Development Board

- 1 x Type-C Data Cable

- 1 x SMA Cable

- 1 x FM Telescopic Antenna

- 1 x Metal Shell